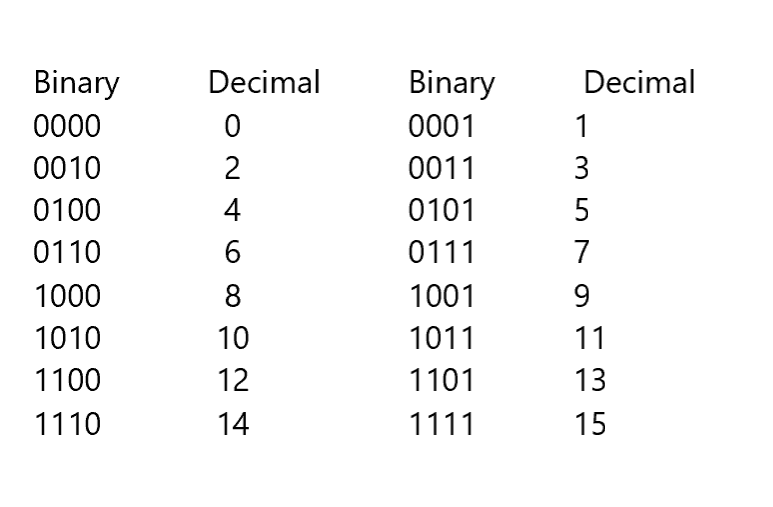

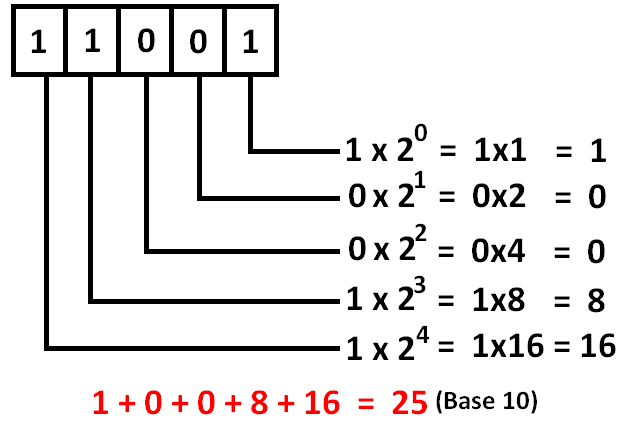

To express the number of integer and fractional bits we use Q number format: Qi.f where i is the number of integer bits and f is the number of fractional bits. See later in this post if you have existing integers you need to convert to fixed point. We’re choosing to interpret the value as being fixed point, but from an FPGA logic point of view, it’s just an 8-bit integer: provided we are consistent in the position of the fixed point we’ll get the expected result from mathematical operations. Or, with a handy point to mark the fractional part: 0100.1100. In binary terms this can be visualized as: We can do the same thing in binary and use the bits to represent any powers of two we like.įor example, we can think of 4.75 as being 4 + 1/2 + 1/4. 1001 is one thousand and one, whereas 10.01 is ten and one hundredth. With decimal numbers, we’re used to the idea of using a decimal separator, a point or comma, to separate integer and fractional parts. In a regular binary integer, the bits represent powers of two, with the least significant bit being 1.įor example, decimal 13 is 1101 in binary: 8 + 4 + 1 = 13. Fixed-Point Numbers in Verilog (this post) - precision without complexity.Multiplication with FPGA DSPs - efficient multiplication with DSPs.Vectors and Arrays - working with Verilog vectors and arrays.Numbers in Verilog - introduction to numbers in Verilog.Share your thoughts with on Mastodon or Twitter. New to the series? Start with Numbers in Verilog. Furthermore, most FPGAs have dedicated DSP blocks that make multiplication and addition of integers fast we can take advantage of that with a fixed-point approach. You could use a library or IP block, but simple fixed point maths can often get the job done with little effort. There is probably a more optimal way to do feedback limiting.Sometimes you need more precision than integers can provide, but floating-point computation is not trivial (try reading IEEE 754). The current stats are 185 logic elements and a 56.61 MHz max clock frequency on a Cyclone I. The flat bottom is about -93 dB.Įdit: The amplitudes on the graphs are relative to the 1 kHz amplitude now, not 20 kHz. On the other hand, the input data is only 16 bits, which is 96 dB dynamic range at best. From what I understand of the the theory, the noise should get lower and lower until it spikes at DC due to a natural offset created by the noise shaping process. I'm still not sure why the low frequency noise floor doesn't look better. I also haven't figured out the optimal limit range for the feedback.ĭropping the input down by 6dB clears out the distortion completely: There is still some distortion, but it is much better than before. Here is the new output spectrum for a 1 kHz full-scale sine wave input: I set it to about 60% of full scale, and the majority of the noise/distortion faded out.

This is recommended in "Principles of Digital Audio," but it doesn't give a specific value. It was even worse with a 1 kHz tone, but the solution was just to stick a limiter inline with the feedback. The (x ? y : z) conditional statements work for assign/wires also.Īs the input wave gets near the extreme ranges of the converter, the feedback has a tendency to go off into the weeds and make bad things happen. Hey, just for code clarity (which also helps find bugs), non-blocking assignments for combinational logic isn't a good idea. That depends on the simulation timescale (for your frequencies `timescale 1ns/1ns should be fine). just as combinational logic, it might not be happening exactly how you would like it to be. Output reg signed d_out //Flip flop outputĪssign delta = (d_out>256) ? INVAL - 15 : INVAL + 15 Īssign feedback = (d_out>256) ? 15 : -15 ĭ_out quant_nef > FB etc. Output wire signed feedback, //Feedback from comparator Output wire signed delta, //Difference signal Input unsigned INVAL, //input value, 0 to 15 I attempted a quick literal translation into Verilog like this: I started with this diagram of a digital first order converter that I found online:

I'm trying to work my way up to a second order sigma delta D/A from scratch. It might not be possible to do decent quality A/D using only an FPGA, but a decent quality sigma delta D/A seems reasonable. Mark the topic unread :: View previous topic :: View next topic

Register Profile Log in to check your private messages Log in Chat Roomįorum index » DIY Hardware and Software » Microcontrollers and Programmable Logic FAQ Calendar Search Memberlist Usergroups Links

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed